A. Tujuan :

- Memahami Dasar kerja Counter dengan menggunakan JK FF

- Memahami rangkaian dan kerja Counter Up

- Membangun rangkaian Counter

B. Alat dan Bahan :

- Komputer atau Laptop

- Software Proteus ISIS sebagai simulator percobaan

- Clock

- JK FF

- Resistor 220 Ohm

- Lampu LED

- Logic Probe

C. Dasar Teori

- Rangkaian Counter merupakan dasar alat penghitung sistem digital. counter dapat dibangun dengan menggunakan FF JK 4 Bit untuk 1 Digit. Rangkaian counter ada 2 macam : yaitu counter Up dan Down. Counter Up untuk mengitung Naik, contoh : jam Digital, Stop Watch, dan lain lain. Counter Down adalah menhitung turun, contoh : Timer Dll.

D. Prosedur Kerja Praktek

- Persiapkan alat dan bahan

- Pahami gambar kerja

- Buat rangkaian sesuai gambar

- Periksa hasil rangkaian

- masukan sumber tegangan jika rangkaian sudah benar

- Lakukan uji coba rangkaian

- Lakukan pengamatan hasil sesuai perintah

- Catat hasilnya sebagai laporan dan dokumen

- Bongkar rangkaian juka sudah selesai

- Kembalikan alat dan bahan ke petugas

- Rapikan dan bersihkan tempat kerja sebelum anda tinggalkan

- Tertip

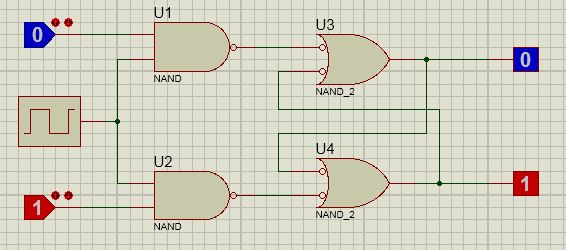

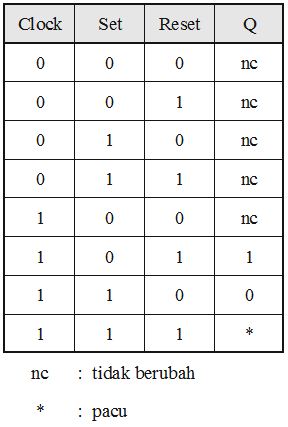

E. Gambar kerja :